Low power design is a system that uses a collection of techniques and methodologies to optimize battery life and reduce the overall power dissipation of the system. Many low-power techniques depend on the level of the design selected, ranging from semiconductor technology to higher levels of abstraction, to optimize power. These abstraction levels are classified as system, algorithm, architecture, circuit, and process levels, which we will discuss further in the article. We will also examine some information on reducing power consumption on embedded systems. Then, in a future article, we will discuss the features of the microcontroller-based low-power system and how you can use them to extend your battery life.

Terms

Before we go any further, we should know these terms:

Current measures the amount of electrical charge transferred per unit of time through a closed circuit. The standard unit is amperes, defined as coulombs (a unit of charge) per second.

I=Q/t

Power (electric power) (P) is the rate at which work is done or energy is transformed into an electrical circuit.

P = VI

Where V is the potential difference in the circuit and I is the electric current through the electric circuit

Energy is the ability to do work. If the power is constant over the time interval then the energy can be expressed simply as:

E = Pt

If power consumption is constant, energy consumption will be power * time during which power is consumed. Reducing power consumption will only save energy if the time required to complete the task does not increase.

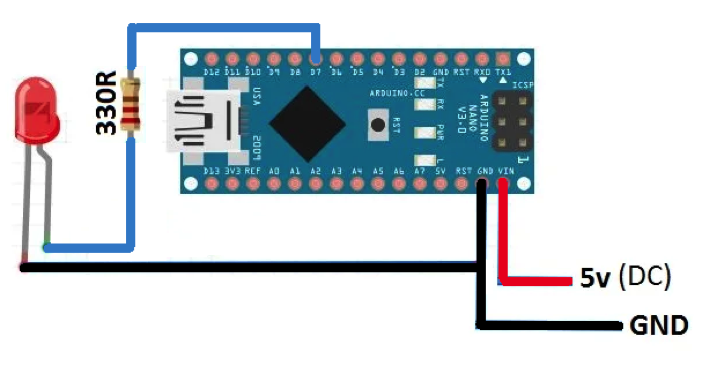

Let’s understand low-power embedded systems by experimenting with LED brightness. Our aim is to demonstrate how an MCU can drive load on low power.

Setup

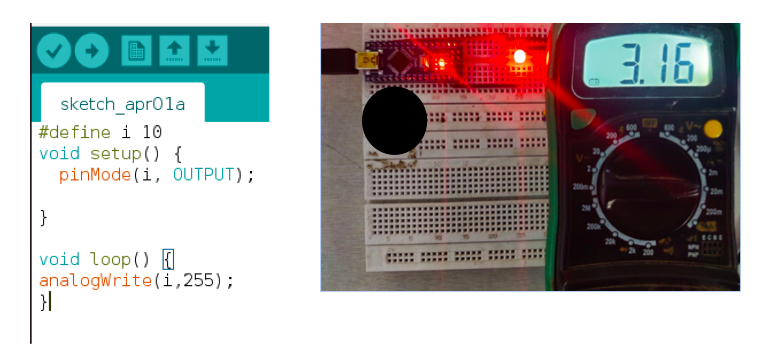

Here, we used an Arduino to control the brightness of the LED. Arduino provides PWM (pulse width modulation) that periodically outputs HIGH and LOW. The PWM function, periodically switching between HIGH and LOW at a specified rate, can adjust the LED brightness.

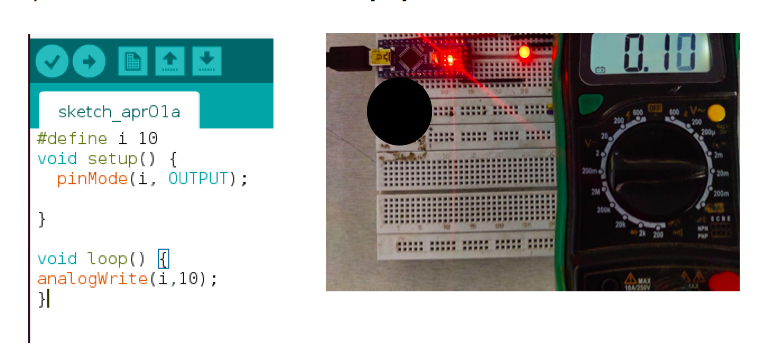

Code explained

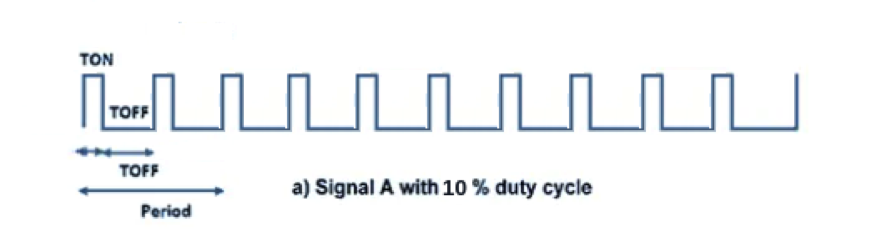

To create a PWM signal, we use the function analogWrite(x, y), where x is the digital pin and y is a value for the “duty cycle” between “0 and 255,” where 0 indicates 0% duty cycle, and 255 indicates 100% duty cycle. This means that when the PWM ratio reaches 255, it is decreased until it reaches 0 to darken the LED gradually.

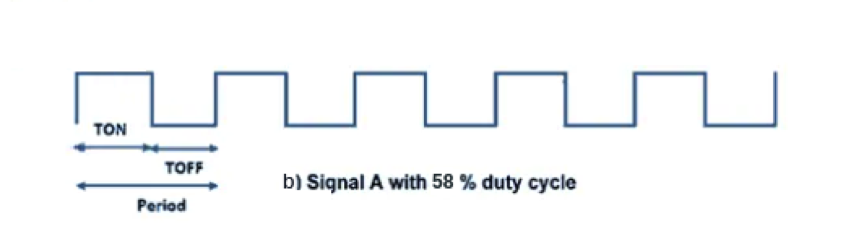

The duty cycle is the ratio of time a load or circuit is ON compared to the time it is OFF. A signal with a 60% duty cycle is ON 60% of the time and OFF 40%.

Test 1

Done when the PWM ratio is ten, and the duty cycle is 4%.

The LED’s low brightness (10 %) uses less drive current, which means less power is consumed. With a 100mA battery and a load of 0.1mA, the run time will be 1000 hours.

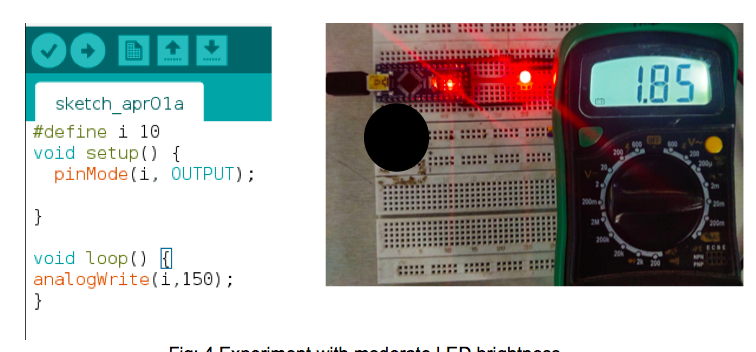

Test 2

Done when the PWM ratio is 150, and the duty cycle is 58%.

The LED’s half brightness (58 %) uses the half drive current, which means half power is consumed. With 100mA of battery and a load of 1.85mA, the run time will be 54 hours.

Test 3

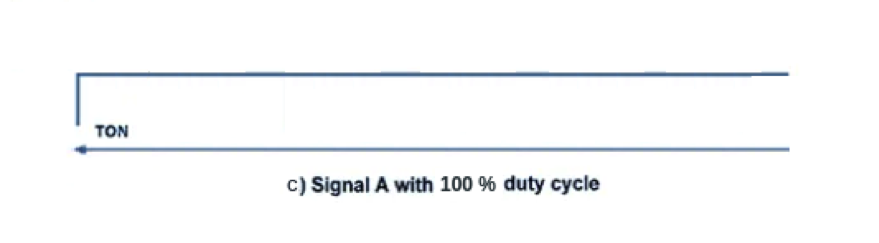

Done when the PWM ratio is 255 and the duty cycle is 100%.

The full brightness of the LED (100 %) uses the full drive current, which means more power is consumed. With 100mA of battery with a load of 3.16mA, the run time will be 31 hours.

The current is proportional to the LED brightness. So, the current is less if the LED’s brightness is less, implying that low power consumption will equal low energy consumption.

Why do we need low-power design?

Embedded systems must be energy efficient during operation to ensure a long battery lifetime, reduce utility power consumption, and prevent excess heat generation. The longer battery life of a product can also lead to lower maintenance costs, as costly visits to replace batteries occur less frequently. Additionally, portable devices such as cellular phones, gaming consoles, and battery-powered electronic systems demand microelectronic circuits designed with ultra-low power dissipation. For example, metering solutions like automatic meter reading (AMR) require more extended battery life and portability as they must be fixed on every meter. They should run about 8- 10 years after the installation.

Levels of power optimization

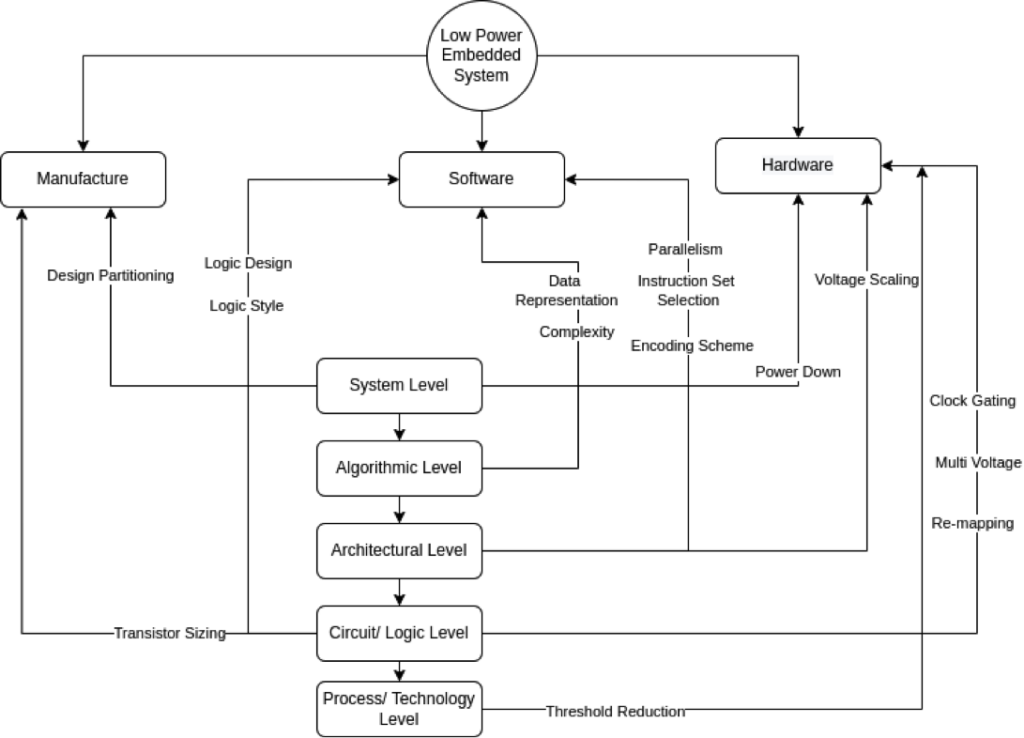

The low-power design of any system is a combination of optimized manufacturer, software, and hardware. In these combinations, power reduction can be implemented at different levels of design abstraction: system, architecture, algorithms, circuit, and the process level. The most efficient design decisions derive from choosing and optimizing architectures and algorithms at these levels. Let’s discuss these levels briefly on which energy reduction can be incorporated:

System level: This level includes the power optimization techniques which can be done at the time of manufacturing of ICs and also at the hardware level. For example, design partitioning is the practice of dividing a system on chip (SoC) into small blocks done on the manufacturer’s side. This allows users to efficiently manage semiconductor designs as a related set of functional blocks. Semiconductor designs are most efficiently managed as related sets of functional blocks.

Algorithmic level: In this technique, the number of operations that require larger power is reduced and basically part of the software; this approach reduces the number of operations and hence reduces the number of hardware resources. For example, most DSP (digital signal processing) algorithms involve several multiplication operations. Multiplication is the most power-consuming operation in such algorithms. It can be replaced by shift-add (this method adds the multiplicand X to itself Y times, where Y denotes the multiplier) operations to reduce power.

Architectural level: Architecture level measures include smart power management of various system blocks, utilization of pipelining and parallelism, design of bus structures, and voltage scaling. At this level, the power reduction can be done on both the hardware and software side. For example, energy consumption in CMOS circuitry is proportional to capacitance. While designing the PCB, we can minimize the bus length by optimal module placement, which will reduce the capacitance.

Logic/circuit design level: This level includes the power optimization techniques which can be done at the time of manufacturing of ICs, hardware, and the software side as well. For example, transistor sizing is the process of reducing or increasing the channel width of the transistor at the time of manufacturing. The smaller the transistors, the more transistors can fit on a chip, and the faster and more efficient the processor can be. Another example is to use a custom design at the hardware side in which components in a circuit used are more static than dynamic.

Process level: This level includes power optimization techniques that can be done only on the hardware side of the system. For example, multi-supply voltages are being used in different functional blocks of the core to save power. Reducing a supply voltage from 5.0 to 3.3 volts (a 44% reduction) reduces power consumption by about 56%.

**We will discuss these in detail in a future article.

Power modeling

Power modeling is a technique or procedure for studying the power generated, lost, and distributed in a system. It helps record past data on power flow and prepare future plans and system designs.

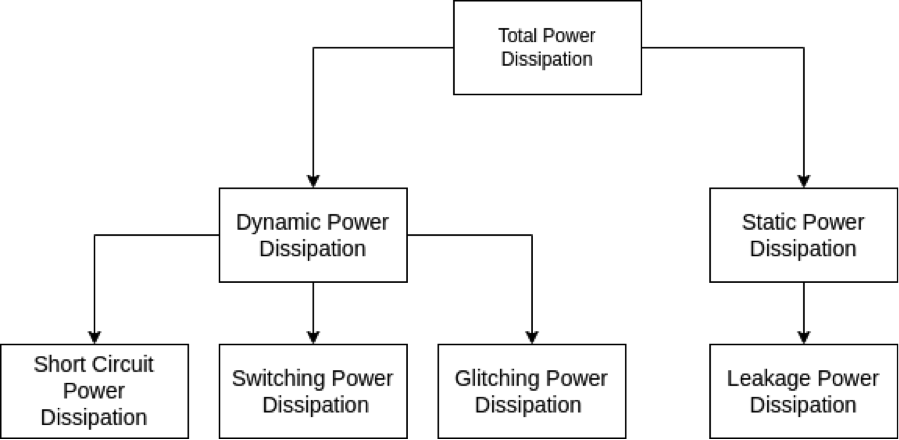

In power modeling, the total power dissipation (PT) can broadly be divided into the following:

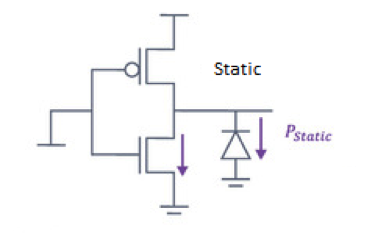

Static power dissipation (PS): Power consumed during a standby mode (when the microcontroller is in sleep mode but LDO (low drop out) is active and consumes power).

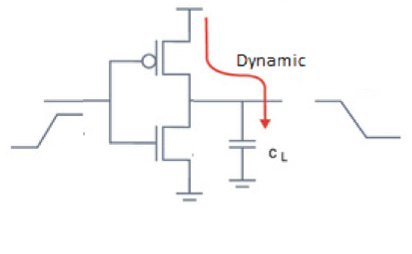

Dynamic power dissipation (PD): Power dissipation occurs during signal switching at the cell input and during the discharging of the capacitances in the circuit. Switched capacitance is the primary source of dynamic power consumption and arises from the charging and discharging of capacitors at the circuit’s outputs.

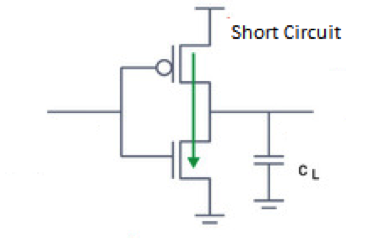

Short-circuit power dissipation (PSC) is a secondary source of dynamic power consumption in which power is dissipated by an instantaneous short-circuit connection between the supply voltage and the ground at the time the gate switches state, which can cause dissipation of more than 20% of the total power.

PT = PS + PD + PSC

Low-power embedded system applications

These include the following:

- Low maintenance Devices

- Digital wristwatches

- Fitness tracker

- Interactive Kiosks

- Beacons

- Cameras

- Mobile Phones

- Unattended Internet-of-Things (IoT) systems

Leave a Reply