Proper sequencing of the multiple power rails in a system is a critical function and can be accomplished using different approaches.

For applications with many rails, complicated sequencing requirements may require many additional components. There are two paths to resolving this advanced sequencing challenge, both offering the needed capabilities. One is based on a user-programmed microcontroller; the other uses a fully programmable but hard-wired IC, which is designed for sequencing.

For example, a power sequencer using a member of the Microchip Technology microcontroller PIC16F1XXX family can handle four, eight, or more power sources (Figure 1). The embedded firmware is user programmed for desired sequencing attributes, along with power-good criteria, ramp-up time, and ramp-down time, as well as implementing various alarm modes if a supply goes out of range or fails.

The PIC-based approach has a 10-bit ADC but digitizes each rail 16 times and then averages the result, yielding the equivalent of a 14-bit conversion. Depending on the specific member of the PIC16F1XXX family selected, the number of general-purpose I/O (GPIO) pins for enabling a voltage regulator or driving a rail MOSFET can be in the dozens and thus capable of handling almost any situation.

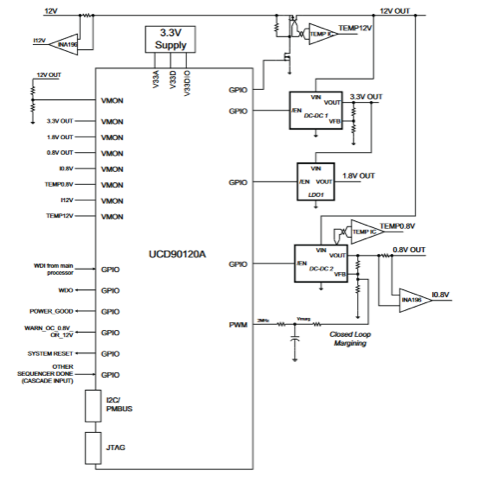

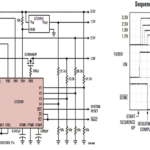

For a sequencing-specific device, UCD90120A from Texas Instruments offers another fully programmable approach (Figure 2). A PMBus/I2C interface addresses this 12-rail power-supply sequencer and monitor and also includes twenty-six GPIO pins, which are available for other supply-related functions, such as generating supply enables, resets, and alarm interrupts to the system processor. When combined with a suitable graphical user interface (GUI), it can be used for establishing complicated power-on/off sequences and timing, providing insight for system-failure analysis if a brownout occurs (Figure 3).

Digital power and power sequencing: opportunities and risk

Basic DC regulators use all-analog or mixed-signal circuitry, whether they are LDOs (still very widely used) or switching regulators. That’s the way most regulators have been implemented for decades, admittedly with many enhancements to (and variants of) both topologies.

If they have a “digital” aspect, it is the use of digital control to set analog-loop parameters such as gain, response, output voltage, current limits, and similar via a PMBus or I2C interface. Once these factors are set in place, the regulator closed-loop operation is an analog function, and even when they are changed or updated via the control bus, the new operating mode is still mostly analog.

However, higher-power systems now often use all-digital power regulation for many reasons. This fully digital power control goes far beyond just setting analog loop parameter via a digital bus. Instead, the actual closed-loop regulation function is executed via digital circuitry including a processor and embedded algorithms.

In these supplies, the output voltage rail is digitized at high speed, compared by firmware to the desired value, which then issues commands to a loop DAC to adjust that output (taking many other factors into account, of course). Sequencing is part of the embedded firmware’s many tasks.

The all-digital approach also allows tailoring of the control and sequencing strategy to better match the operating conditions, and the user to specify what supply tradeoffs are preferred at different points of operation: improved regulation, increased efficiency, lowest electrical noise, and more. Even better, these priorities can be dynamically changed as needed. It’s the ultimate in flexibility with the ability to adjust as needs and priorities change — an engineer’s dream situation, in many cases.

Even the sequencing is an inherent part of the digital control algorithm for the various rails, and so can also be flexible and adjusted as well. Given all these benefits and the inherent flexibility, there should be no hesitation in adopting digital power and sequencing. After all, why commit when you can be flexible?

But sometimes, too much of a good thing can be a potential problem. When almost everything in a design is software-driven and thus can be changed without too much pain, there are consequences when thinking about and executing the project:

First, there’s a tendency to think, “Just ship it; we can fix it in software later.”

Second, it’s often hard to know what you actually have since the documentation of the changes may be incomplete, and even a code listing won’t help; you really need to know the intent of the code blocks and the algorithms.

Third is that having flexible and changeable code in the power supply rails and sequencing means that the design has yet another function which is “fluid.” Yet experienced designers know that one of the key steps to keeping a project moving ahead is to “nail down” as many aspects as possible, especially those that have system-wide implications. When everything is malleable and subject to change, trying to make progress can be like trying to nail Jell-O to a wall.

Finally, the fact that the sequencer itself is a processor-based IC running code means that it must start up properly prior to any of the other rails or components becoming fully active. In other words, it would become a race between the sequencer being ready to do what it is supposed to do versus the regulators and rails the sequencer is managing reaching their nominal values before they have been properly sequenced and managed. In these designs, therefore, it’s critical to have all the rail regulators remain in a quiescent state on system power up until they are directed to become active.

An important system-level decision is whether to use firmware-based sequencing with its inherent flexibility or use a hardwired sequencing IC that is guaranteed to “instantly” do what it is designed to on power up. The power-supply subsystem’s design and performance are some of the best places to make a firm design decision and then leave it alone.

After all, a solid, clean, low-noise, consistent supply network is literally and figuratively a foundation that supports all the other subsystems in the design to function. In contrast, a supply that has marginal performance or unusual dynamic characteristics can exhibit strange problems that manifest themselves in inexplicable ways; often, a supply-rail problem looks like a software bug (don’t ask how we know this!).

If the decision is not carefully evaluated with respect to the design risks, the power subsystem could become another chameleon-like “loose end” with which the design team is trying to catch up, figure out what it is doing, and grasp the implications of the latest changes.

Conclusion

Power supplies and their rails may not have the glamour or get the attention that processors or wired/wireless communication links and interfaces receive. However, they are an i important function of a successful, reliable design in high-capability, high-performance designs ranging from handheld smartphones and instrumentation to server farms and data centers.

Managing the disparate rails is not an easy task, but many options for power-supply sequencing and PMICs are available that match features to project requirements. These solutions range from simple cascaded sequential IC Enables to sophisticated, fully programmable ICs with advanced functions, offering the ability to establish and change the values of many key parameters.

Related EE World Content

If you’re designing power ICs, here are some tools to consider

Selecting and applying programmable power supplies

Device Enables Fault-Proof Sequencing Of FPGA Power Rails

Supervisory ICs tame power-up glitch headaches, Part 1

Supervisory ICs tame power-up glitch headaches, Part 2

External References

Texas Instruments, “Power-supply sequencing for FPGAs”

Analog Devices, “Power Supply Sequencing Simplified”

Analog Devices, “Complex Power-Supply Sequencing Made Easy”

Advanced Micro Devices, Inc., “Simplified Power Sequencing”

Microchip Technology, Inc., “Why Is Power Sequencing Needed?”

Leave a Reply