Researchers in Sweden have come up with a way of putting gallium-nitride transistor structures on a silicon-carbide substrate that potentially lowers the ON resistance of power FETs by an order of magnitude below that of commercial devices available now.

The scientists hail from Sweden’s Linköping University and SweGaN, a spin-off company from materials science research at LiU. The new transistors use what’s called a QuanFINE structure and an epitaxial growth mechanism called transmorphic heteroepitaxy. This new growth mechanism prevents structural defects from forming in the beginning of the epitaxy, enabling the creation of grain-boundary-free AlN nucleation layers and subsequent high-quality buffer-free GaN-based heterostructures on SiC substrates.

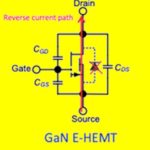

The construction technique builds a high-electron-velocity thin GaN layer produced via MOCVD on the high-breakdown bulk SiC. In the HEMT heterostructure, an AlN nucleation layer serves as a back-side barrier that, along with a front-side barrier, confines the electrons in the thin GaN channel (< 250 nm) in a quantum-well–like structure. The semi-insulating SiC substrate serves as the voltage blocking layer having a resistivity significantly higher than the conventional thick carbon-doped GaN buffer layer used by conventional devices. Moreover, researchers say it also provides superior thermal management thanks to the nearly perfect GaN–SiC interface.

In contrast, the conventional thermal boundary resistance (TBR) arising in ordinary GaN – SiC interfaces causes up to 40% more channel temperature rise in transistors. The ultra-low-TBR AlN nucleation layer all but eliminates this additional temperature rise, scientists say. The structural quality of the thin AlN nucleation layer significantly improves the heat flow from the channel down to the high-thermal-conductivity SiC substrate, making power devices built with the technique more reliable. By reducing the operational temperature by 25°C, the device lifetime rises by a factor of ten.

Scientists described their work in a recent Applied Physics Letters article. They report seeing lateral breakdown voltages of 900 V and 1,800 V at contact distances of 5 and 20 μm, respectively. They say their results are promising enough to suggest that the transmorphic epitaxially grown AlN-layer-on-SiC may become the next paradigm for GaN power electronics.

Leave a Reply