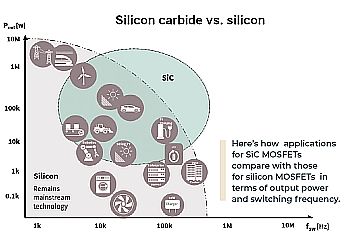

The benefits silicon-carbide MOSFETs become evident from comparisons with their silicon counterparts.

Rene Mente • Infineon Technologies

New 650-V SiC MOSFETs make it practical to hit power conversion efficiency levels exceeding 97% in switched-mode power supply (SMPS) designs. Simply replacing silicon MOSFETs with SiC versions in typical resonant designs will improve efficiency, but the most significant gains come from rethinking designs completely. There are several factors to consider when determining when to opt for a new design approach.

SiC configurations can bring higher power density (and thus smaller footprints, reduced thermal management requirements) that silicon devices can’t provide. The result ultimately can be a lower total cost of ownership (TCO). For an example, consider server/telecom power supplies. Here, higher switching frequencies with SiC MOSFETs bring greater efficiency, a lighter and smaller power supply, higher reliability because of simpler overall topology, and a more economical BOM.

SiC configurations can bring higher power density (and thus smaller footprints, reduced thermal management requirements) that silicon devices can’t provide. The result ultimately can be a lower total cost of ownership (TCO). For an example, consider server/telecom power supplies. Here, higher switching frequencies with SiC MOSFETs bring greater efficiency, a lighter and smaller power supply, higher reliability because of simpler overall topology, and a more economical BOM.

Consider a full-bridge totem pole PFC that utilizes two SiC and two low-ohmic superjunction (SJ) MOSFETs in four-phase operation over each ac cycle. In both the positive and negative phases of the cycle, one of the SJ MOSFETs continuously conducts while the corresponding SiC MOSFETs alternate between conducting (on) and off states. At each of the on/off states there is a short period in which one SiC MOSFET body diode conducts and the second MOSFET is actively turned on. Because of this hard commutation on a conducting body diode, the low reverse-recovery charge and output charge (Qrr and Qoss) characteristics of the SiC devices are a major factor in system efficiency.

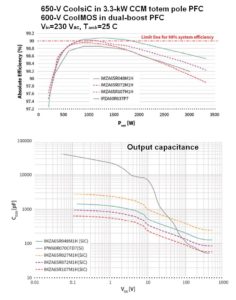

While it’s possible to implement a high-efficiency triangular current-mode (TCM) totem pole using silicon MOSFETS, doing so would require a more complex controller and driving scheme that would raise part count and costs. The most similar topology based on 600-V Si MOSFETs would be a Dual Boost PFC. We can use this configuration for efficiency comparisons with a design employing three variants of a 650-V SiC MOSFET (48 mΩ, 72 mΩ and 107 mΩ). The Dual Boost topology efficiency tops out at 98.85%. All three SiC MOSFETs exceed this mark, and the 48-mΩ device reaches at least 99% efficiency across an output range of 800-1,800 W. It takes a 99% efficient PFC stage to reach a target of 98% system efficiency.

Efficiency comparisons for the LLC resonant converter (the LLC moniker denotes the resonant components), expressed as diode losses, were calculated for a design that substitutes SiC MOSFETs for silicon devices with subsequent optimization of the converter dead-time settings. Efficiency improved by up to 0.5% at light loads. This improvement declined to 0.1% at 10-A output with RDS(on) being the main source of the losses.

Contributing factors

SiC MOSFETs exhibit body diode behavior and linear output capacitance that are well-suited to topologies which have hard commutation on the conducting body diode in every switching cycle. For example, the reverse recovery

charge (Qrr) of the Infineon CoolSiC 650-V MOSFETs is approximately 10 times lower than peak-performing fast diode silicon MOSFETs. This parameter is key in reaching the 99% peak efficiency in the PFC scheme discussed here. It is important to note that the forward voltage of the SiC body diode is a little less than four times higher than that in silicon MOSFETs. Thus, while it is possible to drive CoolSiC MOSFETs as though they were silicon devices, body diode conduction losses can boost efficiency without a change in driving strategy.

The output capacitance (Coss) behavior of SiC varies across output voltage much more linearly than that of silicon MOSFETs. Importantly, the lower capacitance of silicon at higher voltages can be problematic in protecting the switch from voltage overshoot. Designers typically aim for 80% de-rating on the drain-source voltage. Experiments have shown that super-junction MOSFETs require an external gate resistor of 47 Ω during start-up in a LLC converter. The risk of exceeding de-rating guidelines is minimal when using a SiC MOSFET, which needs no external resistor to slow the switching frequency during turn-off in this experiment.

Other important factors contributing to SiC MOSFET performance in this SMPS revolve around the stability of electrical characteristics across operating temperature ranges. For example, RDS(on) remains remarkably stable, with a multiplication factor of 1.13 from 25 to 100°C for a CoolSiC device compared to 1.67 for a CoolMOS silicon device. This behavior allows use of devices having an RDS(on) at 25°C exceeding that of silicon MOSFETs while not sacrificing conduction losses.

The behavior of breakdown voltage across operating temperatures also is favorable; SiC has a shallower and more consistent slope than silicon, with a relatively minor variation from the specified 650 V at 25°C. Current transfer characteristics also are stable across varying temperatures.

Finally, the gate charge is on average 50% lower for this class of SiC MOSFETs compared to silicon devices with the same RDS(on).

Designing with SiC MOSFETs

The decision to use SiC MOSFETs yields the greatest benefit by adopting new strategies for gate driving. Infineon recommends a driving voltage from 0–18 V. Compared to silicon-specific drivers (typically up to 15 V), gate-driving strategies can reduce the RDS(on) by approximately 18%.

A second factor in driver design is the importance of minimizing negative gate-source voltage, which can have two root causes. One is inductance-driven oscillation of gate-source voltage during turn-off. The second is capacitance-driven negative gate-source voltage.

In either case, voltages below -2 V can degrade RDS(on) over the device lifetime. A diode clamp is the

most straightforward way to address negative voltage, and it has been shown to prevent any swing below -2 V, thus eliminating drift over time. Parasitic gate inductance may also impact the negative voltage effect, and this problem can be mitigated with a Kelvin source connection.

With the exception of the gate-driving strategy, key design considerations and constraints faced with SiC MOSFETs are similar to those for silicon MOSFETs.

The additional robustness of SiC makes the newly available devices inherently easier to use. Thus, for high power applications where the design goal is greater than 97% system efficiency, 650-V SiC MOSFETs are on track to simplify things for power supply suppliers.

Leave a Reply