By Suzana Jankuloska, Aluminum Electrolytic Product Manager at KEMET Corp

Electrolytic capacitors optimized for low internal inductance can help reduce the cost of industrial power-conversion applications while increasing efficiency, performance, and reliability.

As the automation of manufacturing and assembly processes continues to become more widespread, driven by emerging trends such as Industry 4.0 and the Industrial Internet of Things (IIoT), low-inductance electrolytic capacitors can help unleash cost savings and performance gains in robots and other industrial equipment.

Polypropylene film and electrolytic capacitors are both suitable for bulk smoothing and decoupling duties in high-power industrial applications, such as at the output of switched-mode power supplies and to stabilize the DC link of variable-frequency motor drives and fixed-frequency generators. Electrolytic capacitors provide high capacitance within small case sizes and at low cost relative to other capacitor technologies and are often preferred in applications up to about 600 V.

Polypropylene film and electrolytic capacitors are both suitable for bulk smoothing and decoupling duties in high-power industrial applications, such as at the output of switched-mode power supplies and to stabilize the DC link of variable-frequency motor drives and fixed-frequency generators. Electrolytic capacitors provide high capacitance within small case sizes and at low cost relative to other capacitor technologies and are often preferred in applications up to about 600 V.

Every real capacitor has an associated inductance that will induce voltage spikes as high-frequency ripple currents pass through the device. Capacitors designed to have low parasitic inductance can reduce the magnitude of these voltage peaks, allowing designers to specify power semiconductors of lower voltage classes. Also, specifying low-inductance devices can reduce the number of individual capacitors needed per bank, helping to lower overall cost and reducing size and weight.

Parasitic inductance of capacitors

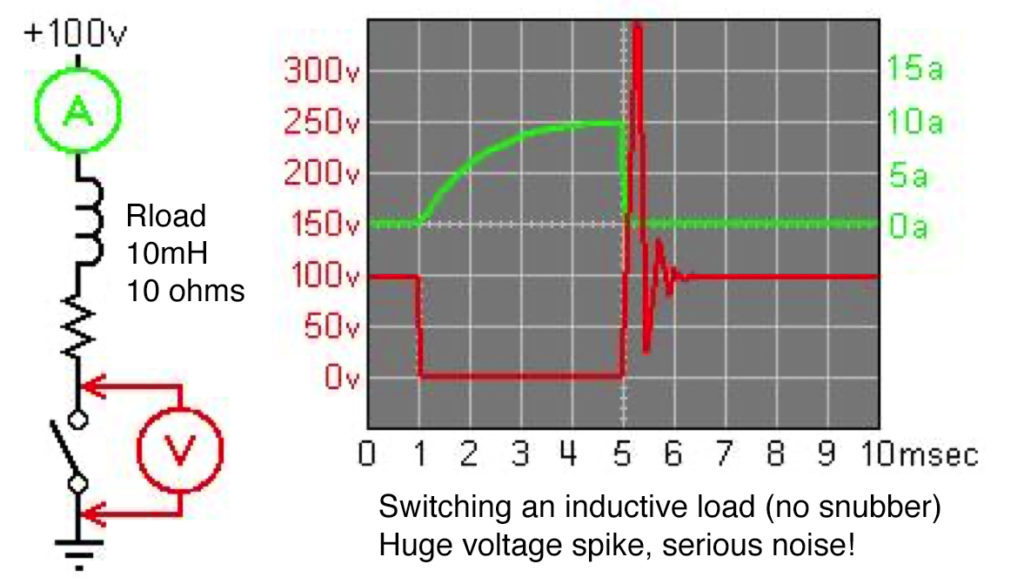

Unlike an ideal capacitor, which can transfer all its stored energy into a load instantaneously, a real capacitor has unwanted parasitic elements that can be modeled as an equivalent inductance and resistance in series with the capacitance (ESL and ESR). The effects of this unwanted inductance include induced voltage spikes, which can damage sensitive components connected to the circuit. Moreover, the interaction between the stray inductance and the device’s capacitance causes noise that can compromise circuit stability and power quality.

In general, inductance tends to oppose changes in current. The magnitude of the effect is dependent on frequency. Whereas capacitive reactance decreases with frequency, inductive reactance tends to increase. These two reactances become equal and opposite at the capacitor’s self-resonant frequency, creating a cancellation effect so that the overall reactance is zero and the capacitor’s impedance is solely due to the ESR:

The component behaves as a capacitor below this self-resonant frequency, and the impedance tends to reduce with increasing frequency. As frequency increases, the impedance characteristic begins to deviate and reaches a minimum at the self-resonant frequency. Above this frequency, the inductive behavior dominates, and the impedance increases. Reducing the capacitor’s ESL raises the self-resonant frequency.

Demand for low-inductance capacitors

Applications that can benefit from low-inductance electrolytic capacitors include bulk capacitance, which is often affected by high-frequency switching. In addition, low-ESL capacitors are desirable for DC-link applications, such as industrial inverter drives, to minimize self-heating while enhancing protection for power devices. The ESL of a standard electrolytic DC link capacitor can contribute along with other connections, cables, and other components to voltage spikes that require a snubber to be placed across each inverter phase leg. Lowering the ESL of the capacitor could lower the overall inductance to the point that could eliminate the need for snubbering circuits across each inverter phase leg.

Internal capacitor design

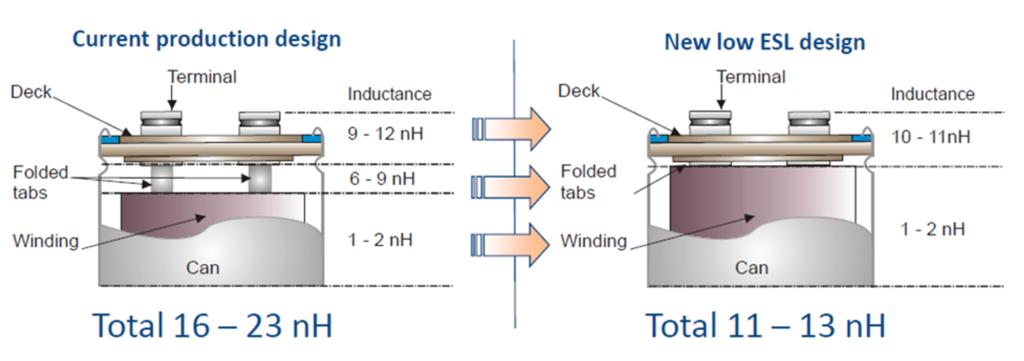

The main internal components that contribute to the ESL of large screw-terminal electrolytic capacitors are the deck terminals, the internal connecting tabs, and the winding, as shown in Figure 1. The ESL can be effectively reduced by optimizing the internal layout to cancel out all magnetic fields generated by the capacitor current. This is achieved by reducing the distance between the wound element and the terminal and reducing the distance between the tabs. Figure 1 compares the internal layout of a standard capacitor with a low-inductance model, showing how the redesigned features lower the inductance by as much as 40%.

Optimized terminal design

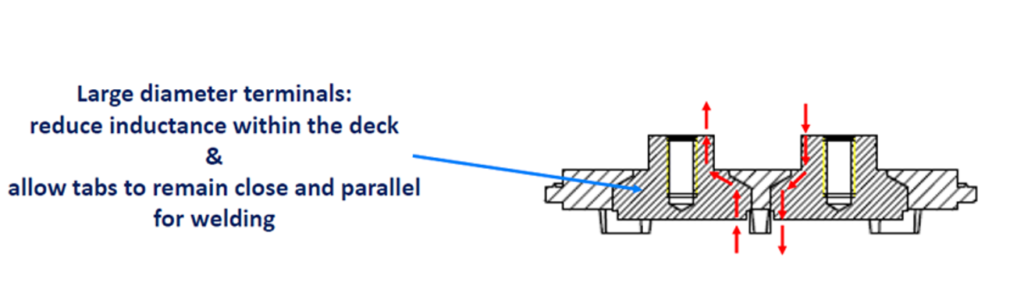

Reducing the spacing between the terminals, as shown in Figure 2, introduces an inductance-canceling effect. Also, the height of the terminals is reduced to shorten the overall conductor length. The larger surface area on the terminals’ underside allows closer spacing of the internal connecting tabs to maximize the cancellation effect. The design also takes advantage of multiple tabs that are all connected in parallel.

Low-inductance capacitors in action

Lowering the entire circuit’s inductance, of which the electrolytic capacitors are a contributing factor, can reduce the amplitude of voltage spikes on power lines (Figure 3). The peaks caused by steep-edged pulses are the most significantly reduced. Reducing the peak voltage on power lines delivers several advantages, including allowing designers to specify power semiconductors of lower voltage rating and, hence, achieving cost savings and increasing power density. In addition, capacitor banks can be constructed using fewer capacitors to achieve the same performance, thereby lowering the cost, weight, and frequency converters’ space requirements.

Conclusion

Reducing the ESL of power capacitors can trim the bill of materials in industrial automation, robotics, power management, and smart-factory equipment. Lowering ESL raises the capacitor self-resonance frequency, enabling use in circuits at higher switching frequencies and reducing peak voltage spikes allowing the use of lower-rated power semiconductors. By reducing noise, lower ESL contributes to improving power quality at the output of switched-mode power supplies.

Low-ESL electrolytic capacitors embody design innovations to reduce the length of interconnects and take advantage of inductance canceling. The % of ESL reduction is maximized at higher voltages. Improvements of up to 40% ESL from the capacitor were measured.

About the author

Suzana Jankuloska is a Product Manager for Electrolytic Capacitors in the Americas. She has been with KEMET since 2012. She is an enthusiast of market and technology trends, specifically those requiring high voltage electrolytic capacitors. Working closely with the KEMET Innovation Center in Portugal, the team pushes the current technology limitations to meet new challenges, and customer needs now, and for the future Suzana earned a degree in Electrical Engineering from the University of Saint Cyril and Methodius in Skopje, Macedonia.

Suzana Jankuloska is a Product Manager for Electrolytic Capacitors in the Americas. She has been with KEMET since 2012. She is an enthusiast of market and technology trends, specifically those requiring high voltage electrolytic capacitors. Working closely with the KEMET Innovation Center in Portugal, the team pushes the current technology limitations to meet new challenges, and customer needs now, and for the future Suzana earned a degree in Electrical Engineering from the University of Saint Cyril and Methodius in Skopje, Macedonia.

Leave a Reply